1. 论文信息

- 文章来自18th USENIX Conference on File and Storage Technologies, (FAST), 2020

- An Empirical Guide to the Behavior and Use of Scalable Persistent Memory

所有作者及单位

- Jian Yang, Juno Kim, Morteza Hoseinzadeh, Steven Swanson. 加州大学圣迭戈分校UCSD

- Joseph Izraelevitz. 科罗拉多大学博尔德分校

2. Background

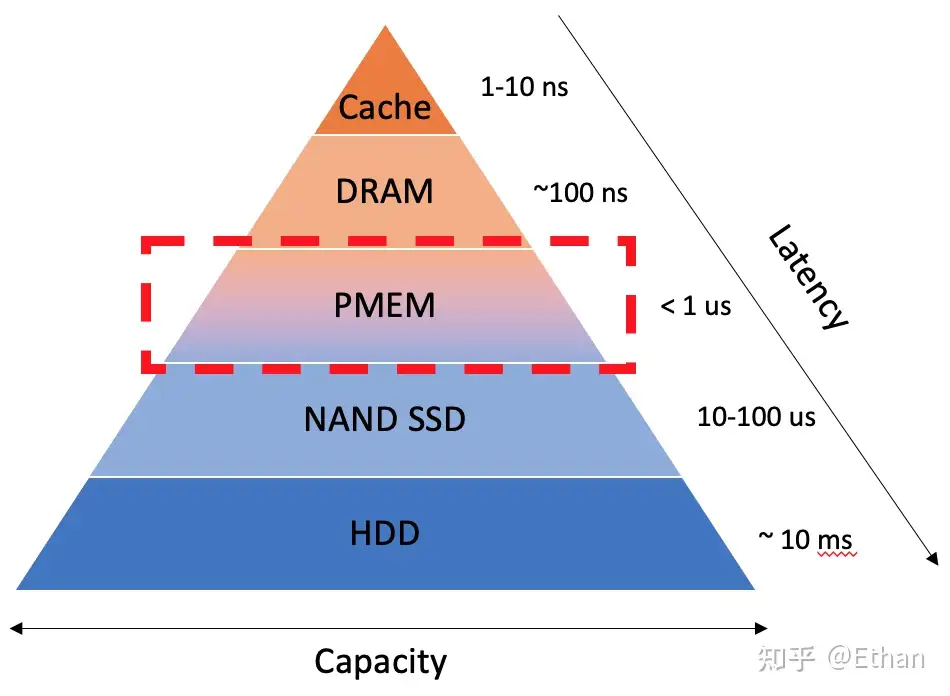

Optane DIMM这种新型非易失性DIMM支持字节粒度访问,访问时间与DRAM相当,同时还提供断电后仍可保存的数据存储。在过去的十年中,研究人员撰写了大量论文,提出了新的编程模型、文件系统、库和应用程序,旨在利用NVDIMM承诺提供的性能和灵活性。这些论文得出结论并做出设计决策,但没有详细了解真正的NVDIMM的行为方式或行业如何将它们集成到计算机架构中。现在我们可以为这些系统的程序员提供详细的性能数据和具体指导,重新评估现有技术的性能,并为真正的Optane DIMM重新优化持久内存软件。

3. 解决了什么问题

从微观和宏观层面探讨了英特尔Optane DIMM的性能特性。特别注意其性能相对于传统DRAM或过去用于模拟NVM的其他方法的特殊性。

我们发现Optane DIMM的实际行为比“较慢、持久 DRAM”标签所暗示的更为复杂和细致。与DRAM性能相比,Optane DIMM性能更依赖于访问大小、访问类型(读与写)、模式和并发程度。此外,Optane DIMM的持久性与英特尔最新处理器提供的架构支持相结合,为软件设计人员带来了更广泛的设计选择

根据这些观察结果,我们推荐了一组最佳实践,以最大限度地提高设备的性能。随着我们加深理解,我们随后探索并重新优化持久内存应用级软件中现有技术的性能。

4. 围绕该问题作者如何构建解决思路

4.1 Optane DIMM架构详细信息

当PM做内存:直接访问(Direct Access,DAX) 机制是一种支持用户态软件直接访问存储于持久内存(Persistent Memory,PM) 的文件的机制,用户态软件无需先将文件数据拷贝到页高速缓存(Page Cache)

与传统DRAM DIMM一样,Optane DIMM位于内存总线上,并连接到处理器的集成内存控制器(iMC)。英特尔的Cascade Lake处理器是第一个(也是唯一一个)支持 Optane DIMM的CPU。在此平台上,每个处理器包含一个或两个处理器芯片,其中包含单独的NUMA节点。每个处理器芯片有两个iMC,每个iMC支持三个通道。因此,处理器芯片总共可以在其两个iMC上支持六个Optane DIMM。

为了确保持久性,iMC位于异步DRAM刷新(ADR)域内Intel的ADR功能可确保到达ADR域的CPU stores能够在电源故障中幸存下来(即,将在保持时间内刷新到NVDIMM,<100 µs)。 iMC为每个 Optane DIMM维护读取和写入挂起队列(RPQ和WPQ)(图1(b)),并且ADR域包括WPQ。一旦数据到达WPQ,ADR将确保iMC在电源故障时将更新刷新到3D-XPoint介质。ADR域不包括处理器缓存,因此存储仅在到达WPQ后才会持久。

iMC使用高速缓存线(64字节)粒度的DDR-T接口与Optane DIMM进行通信,该接口与DDR4共享机械和电气接口,但使用不同的协议来实现异步命令和数据计时。

对NVDIMM(图1(b))的内存访问首先到达DIMM控制器(本文中称为XPController)该控制器协调对Optane介质的访问。与SSD类似,Optane DIMM执行内部地址转换以进行磨损均衡和坏块管理,并为此转换维护一个地址间接表(AIT)。地址转换之后,就发生对存储介质的实际访问。由于3D-XPoint物理介质访问粒度为256字节(本文中称为 XPLine),XPController将较小的请求转换为较大的256 字节访问,导致写入放大,因为小型存储变成了读-修改-写操作。 XPController有一个小的写合并缓冲区(本文称为XPBuffer),用于合并相邻的写操作。

Optane内存可以(可选)跨通道和DIMMs交错使用,如下图:

4.2 Optane DIMM与DRAM的不同之处

这些测量反映了软件看到的加载和存储延迟,而不是这些底层内存设备的加载和存储延迟:

尾延迟是指在读取或写入数据时,一些操作所需的时间明显超过了大多数操作的平均时间。这种情况可能导致一些请求的响应时间明显延长,从而影响系统的整体性能。

99.9百分位延迟:这是在一组操作中,有99.9%的操作所经历的延迟时间的阈值。换句话说,只有0.1%的操作会在这个延迟时间之上。通常,这个度量标志着绝大多数操作的延迟情况,但允许一小部分极端情况的出现。

99.99百分位延迟:这是更严格的延迟度量,表示在一组操作中,有99.99%的操作所经历的延迟时间的阈值。只有0.01%的操作会在这个延迟时间之上。这个度量用于更强调延迟的可靠性,确保绝大多数操作都在非常短的时间内完成。

最大延迟:这是一组操作中的最长延迟时间,表示最慢的操作需要多长时间才能完成。最大延迟是最极端的情况,通常用于评估系统的最坏情况行为。在一些实时应用和服务中,尤其是需要低延迟的情境下,最大延迟非常重要,因为即使只有极少数操作的延迟超出预期,也可能对系统的性能和用户体验产生重大影响。

尾部延迟一项显示顺序写入一小块内存区域(热点)的尾部延迟的实验。Optane内存具有罕见的“异常值”,其中少量写入需要长达50µs才能完成(比通常的延迟增加了100倍)

DRAM带宽不仅高于Optane,而且随线程数可预测(且单调)扩展,直至DRAM带宽饱和,而这在很大程度上与访问大小无关。首先,对于单个DIMM,最大读取带宽是最大写带宽的2.9倍,而DRAM只有1.3倍的差距。除了交错读取之外,Optane性能随着线程数的增加而呈现非单调性。对于非交错(即单DIMM)情况,性能在1到4个线程之间达到峰值,然后逐渐下降。

4.3 Optane DIMM与其他仿真技术的不同之处

这些图中的数据表明,没有一种模拟机制能够捕获 Optane 行为的细节——所有方法都与真实的 Optane 内存有很大的偏差。他们无法捕捉傲腾内存对顺序访问和读/写不对称性的偏好,并对设备延迟和带宽给出非常不准确的猜测。

4.4 Optane DIMM最佳实践

图8绘制了我们系统性地扫描Optane性能的所有测量结果中单个DIMM的EWR和有效设备带宽(dram和cpu之间的!)之间的强相关性。基于这种关系,我们得出结论,努力最大化EWR(Effective Write Ratio)是最大化带宽的好方法。

而且由于最小粒度是256B,但是iMC发出64B的话,就会在缓冲区被合并为256B,所以下图探究了每次写入更新多少大小合适。避免小型的stores超过16KB也不合适。

绘制iMC争用图。在固定数量6个线程的情况下,随着每个线程访问的DIMM数量的增加,带宽会下降。为了获得最大带宽,线程应固定到DIMM。图15说明了当多个核心针对单个DIMM时,iMC中有限的队列容量如何影响性能。该图显示了使用固定数量的线程(24个用于读取,6个用于 ntstore)向6个交错 Optane DIMM 读取/写入数据的实验。我们让每个线程随机访问N个 DIMM(跨线程均匀分布)。随着N的增加,针对每个DIMM的写入器数量会增加,但每个DIMM的带宽会下降。可能的罪魁祸首是XP Buffer的容量有限,但EWR仍然非常接近1,因此性能问题肯定出在iMC上。

避免对远程 NUMA 节点进行混合或多线程访问PM性能下降率与远程DRAM与本地 DRAM的性能下降率类似。然而,当线程数量增加或读/写混合工作负载时,Optane内存的带宽会急剧下降。根据我们的系统扫描结果,相同工作负载下,本地和远程Optane内存之间的带宽差距可能超过30倍,而本地和远程DRAM之间的差距最大仅为3.3 倍。

5.如何扩展到未来几代 NVM

增加或减少 256 B 内部写入大小可能会很昂贵。人们普遍认为Optane是相变存储器,由于功率限制,较小的内部页面尺寸长期以来一直是相变存储器的标志[2]。较小的内部页面大小不太可能,因为由此产生的存储器密度较低。不同的底层存储单元技术(例如自旋扭矩 MRAM)将带来更彻底的改变。事实上,电池供电的 DRAM 是一种众所周知且广泛部署的持久内存技术(尽管可扩展性或成本效益不高)。对于它,我们的大多数指南都是不必要的,尽管由于缓存一致性模型的限制,非临时存储对于大型传输仍然更有效。