1. 论文信息

所有作者及单位

- Reza Salkhordeh and Hossein Asadi, Data Storage Systems & Networks (DSN) Lab, 伊朗谢里夫理工计算工程系

2. Background

3. 解决了什么问题

本文提出了一种在主存储器中同时采用DRAM和NVM的混合存储器架构中的数据迁移方案。所提出方案的主要目的是减少DRAM和NVM存储器之间无益数据迁移的数量,以提高性能和功效。

4. 其他学者解决这个问题的思路和缺陷

与Clock-DWF不同的是,每次写入命中都会导致将页面移动到DRAM主存储器,在所提出的方案中,NVM LRU中的每次命中都将被与LRU算法类似地处理,但有一个区别。如果某个页面停留在LRU顶部页面的时间超过阈值访问次数,则该页面将被视为热页面,并将被移至DRAM。由于在两个存储器之间移动数据页的成本很高,因此使用此阈值将防止在以前的研究(例如Clock-DWF)中很可能发生的无益迁移。

CLOCK-DWF 使用两种时钟算法,每个内存模块使用一种时钟算法。当发生页面错误时,如果导致页面错误的请求是写入,则该页面将被移动到DRAM,否则它将被移动到NVM。时钟算法的修改使 CLOCK-DWF 能够找到活跃的并且写入为主的数据页并将它们移动到 DRAM 内存。如果针对驻留在 NVM 存储器中的数据页的写入请求到达,则该数据页将被移动到 DRAM。在两个存储器之间迁移页面需要对两个存储器进行多次访问。但CLOCK-DWF中没有考虑这种影响,这将导致其模型不准确

5. 围绕该问题作者如何构建解决思路

使用两个最近最少使用(LRU)队列(一个用于DRAM,一个用于NVM),并优化NVM的LRU队列,以防止无益的迁移到DRAM。LRU队列中的优化是最小的,因此所提出的方案将具有与未修改的LRU几乎相同的命中率。

1)建立性能能量模型

18年华科的对象级迁移的性能能量建模就和这个差不多。但是这里的性能能量建模只适用于说明之前方案的缺陷,和后面方案设计没太大关系。

性能模型取决于DRAM和NVM的延迟、驱逐的粒度以及存储器之间迁移的延迟。为了衡量性能,我们使用平均内存访问时间(AMAT)。迁移的开销将在对内存的所有访问之间按比例分配。公式1显示了AMAT 的公式。表I中提供了参数的描述。在该等式中,前两项计算DRAM或NVM中所有命中访问的 AMAT。第三项考虑页面错误。由于将数据页从磁盘传输到内存将通过DMA 完成,因此将数据块写入内存的延迟将与从磁盘读取下一个数据块的延迟重叠。因此,操作系统只看到磁盘延迟,在这个术语中我们只考虑磁盘延迟。最后两项计算两个存储器之间的迁移成本。当发生迁移时,将从一个内存读取数据页并将其写入另一个内存。由于数据页的粒度比对内存的实际访问要大得多(通常为4到16B),因此我们使用PageFactor,它是一个系数,可将数据页的移动转换为要被访问的内存数量。

无论到达存储器的请求数量如何,都会消耗静态功耗,而每个发送到存储器的请求都会消耗动态功耗。我们的电源模型考虑了两个内存之间的迁移以及将页面从磁盘移动到任一内存模块以及服务请求的静态和动态电源。每次访问内存时都会计算动态功耗。这将导致功耗模型独立于应用程序运行时和内存大小。因此,我们引入每个请求的平均功率(APPR)作为测量功率的指标,如公式2所示。与性能模型类似,前两项计算对存储器的所有命中访问的功率。第三项和第四项考虑将数据页从磁盘移动到内存模块的写入功率。最后两项考虑了两个存储器之间迁移的功率效应。

由于静态功耗与请求无关,因此我们引入了一个名为 AvgStaticPower 的新参数,该参数按比例分配给定时间间隔内到达内存的所有请求之间的静态功耗。对所有请求按比例分配静态功耗的原因是,从操作系统的角度来看,主内存会消耗功率(包括静态和动态)来服务请求,并且这两个功耗来源都应被视为服务成本的请求。对于特定工作负载,AvgStaticPower根据公式3计算。

2)迁移方案

为了找到在迁移时能够改善功耗和性能的数据页(相对于迁移成本),所提出的方案存储了一些关于数据页的附加信息,例如NVM LRU队列中的读和写计数器。请注意,此附加信息不会干扰LRU,并且不需要了解此内务信息。对于NVM队列中的每个数据页,将存储两个计数器,用于计数从数据页进入队列时起对相应数据页的读写访问的次数。

图 3 显示了所提出的由两个 LRU 队列组成的数据迁移方案的架构。虚线表示所提出的技术执行的操作,实线表示传统的 LRU 管理算法。暗数据页访问更频繁,被视为热数据页。与 CLOCK DWF 将读取请求发出的页面错误放置在 NVM 上相反,所提出的方案将所有页面从磁盘移动到 DRAM 区域。这是因为移动到 NVM 或 DRAM 将导致 NVM 中的页面写入,因为 DRAM 始终已满,并且将数据页面移动到 DRAM 会向 NVM 发出驱逐。因此,就 NVM 写入而言,迁移到 NVM 或 DRAM 的成本是相同的。与旧数据页相比,新访问的数据页具有更高的访问概率,并且将此新页移动到 DRAM 将导致 DRAM 命中率而不是 NVM 命中率的增加。这将有助于提高性能和电源效率,因为 DRAM 在动态功耗和延迟方面具有优越性。存储内务信息的开销并不大,对于 4KB 数据页来说约为 0.04%。然而,在 NVM 中保留所有页面的计数器有一些缺点。首先,它需要一个排序方案,以便识别冷但会在很长一段时间内访问一次的数据页。这些数据页将在 NVM 中驻留足够长的时间以具有较高的计数器值,因此将被移动到 DRAM,在那里它们无法与热数据页竞争,并且将返回到 NVM,这使得它们迁移到 DRAM 没有任何好处。

算法 1 显示了在收到请求的情况下所提出方案的流程。由于 DRAM 包含最热的数据页,因此所提出的方案首先搜索 DRAM,如果没有找到,则转到 NVM。在 DRAM 中查找数据页将导致正常的 LRU 内务处理。否则,NVM 中的额外内务信息将根据请求类型进行更新。读取和写入计数器将分别存储在 NVM 中的 readperc 和 writeperc 顶部数据页。因此,在命中的情况下,从顶部数据页掉落的数据页的读和写计数器将被清除。第 10 行到第 22 行初始化相应数据页的计数器。如果 NVM 中数据页的计数器值超过读取阈值或写入阈值(取决于请求类型),则会将其迁移到 DRAM。将新数据页插入内存和逐出策略与 LRU 相比没有变化,因此,为了简洁起见,算法中省略了这些细节。读取阈值和写入阈值的值决定了我们计划如何积极地阻止有用概率较低的迁移。它与 DRAM 和 NVM 之间的迁移成本密切相关,而迁移成本又与所采用的 NVM 的性能和功耗特性有关。

6. 从结果看,作者如何有力证明他解决了问题

7. 缺陷和改进思路

8. 创新点

发现了先前研究的缺点,并提出了一种新颖的混合内存数据迁移方案。在LRU上加了一些小改动。

9. 积累

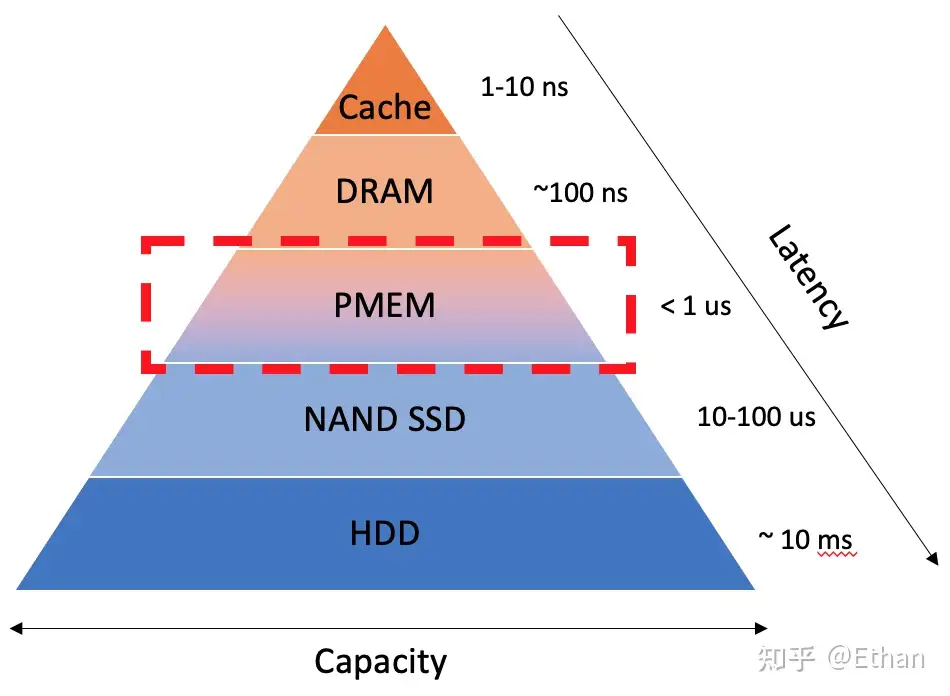

在过去几年提供的各种NVM中,相变存储器(PCM)、自旋转移扭矩(STT-RAM) 和电阻RAM(PRAM)被认为是主存储器中最有前途的NVM[2] 。

本文中我们使用COTSon全系统模拟器[13]。

CLOCK-DWF 维护 DRAM 和 NVM 的两种时钟算法。 NVM中的时钟算法与传统的时钟算法有一点不同。如果对 NVM 中的数据页进行写访问,则相应的数据页将被移动到 DRAM。因此,NVM 不会响应任何写访问。该方法的主要目的是减少 NVM 中的写入次数。虽然这会阻止任何写入到达 NVM,但 NVM 中数据页的每次写入访问都会导致两个存储器之间的数据页迁移。然而,DRAM 的时钟算法有所不同,它尝试将写主导的数据页保留在 DRAM 内存中,并逐出主要读主导的数据页。这是因为与 NVM中的写入请求相比,只读页面具有更好的性能与功耗权衡。发生页面错误时,如果请求是读,则相应的数据页将被移动到NVM,如果是写,则数据页将被移动到DRAM。